Embedded System (MBD)

- Module 1 - Setup

- Module 2 - Introduction to AVR Assembly

- 1. Introduction to AVR Assembly Language

- 2. ATmega328P Hardware & Memory Architecture

- 3. Input/Output (I/O) Programming

- 4. Assembly Integration with Arduino IDE

- 5. AVR Assembly Instruction Set

- 6. Status Register (SREG)

- 7. Delay Implementation Without Library

- 8. Complete Program Examples

- Module 3 - Serial Port

- Introduction to USART

- USART Register Architecture of ATmega328p

- Implementation and Assembly Code Examples

- Module 4 - Arithmetic

- 1. Memory in AVR Architecture

- 2. Addressing Modes

- 3. The Status Register

- 4. Advanced Arithmetic Operations

- 5. The Stack

- 6. Printing Bytes as Hexadecimal Values

- 7. 𝔗𝔥𝔢 ℭ𝔬𝔡𝔢

- 8. References

- Module 5 - Timer

- 1. Introduction to AVR Timers

- 2. Operating Modes

- 3. Timer0

- 4. Timer1

- 5. Delay Using Timers

- 6. Der Code

- Module 6 - Interrupt

- 1. Introduction to Interrupt

- 2. Interrupt Handler

- 3. External Interrupt Registers

- 4. Internal/Timer Interrupts

- Module 7 - PWM and EEPROM

- Modul 8: ADC (Analog to Digital Conversion)

- 1. Analog vs Digital Signal

- 2. Analog to Digital Converter (ADC)

- 3. Why is ADC Needed in Embedded Systems?

- 4. ADC In ATmega328p

- 5. Important ADC Parameters In ATmega328p

- 6. Specific Registers for ADC In ATmega328p

- 7. ADC Conversion Flowchart

- 8. ADC Assembly Code Example

- Module 9 - SPI, I2C, and Sensor Interfacing

- 1. Serial Peripheral Interface (SPI)

- 2. Inter-Integrated Circuit (I2C)

- 3. DHT11 Sensor Interfacing

- 4. SPI vs I2C Comparison

- Final Project

Module 1 - Setup

1. Proteus Installation Tutorial

Step 1 : Install Proteus

If you haven't install. Then Install, remember from DSD.

Step 2 : Download the Arduino Library for Proteus

Download from here : https://drive.google.com/file/d/1LMYOUn39nAZBdGL0SR3n30pf-fRXeP-B/view

Step 3 : Install the Library

Go to the System Settings in System Tab :

And then choose where you extract the downloaded folder :

Step 4 : Install Arduino IDE

Go and Install Arduino IDE from here : https://www.arduino.cc/en/software

2. Proteus Simulation Tutorial

Step 1 : Setup the Arduino IDE

Go to Preferences :

Checklist the Show Verbose output during compile and upload :

Step 2 : Compile the Code

Compile the code using this button :

Find the Hex link on the output terminal :

Step 3 : Connect the Hex

Double click the Arduino on the Simulation :

Copy the hex to the Arduino on the Proteus Simulation :

\

Step 4 : Run the Code

COMPLETE

Module 2 - Introduction to AVR Assembly

1. Introduction to AVR Assembly Language

Assembly is a low-level programming language that allows manipulation of every bit in memory, resulting in highly efficient and fast code. It has a strong one-to-one correspondence with the machine code instructions of the computer architecture.

On Arduino microcontrollers (specifically the ATmega328P), Assembly programming enables high-level control suitable for real-time systems and applications requiring complex mathematical processes.

Advantages of Using Assembly:

- High efficiency: Full control over memory usage and execution time.

- Deep understanding: Helps understand fundamental microcontroller operations.

- Problem solving: Can solve problems that may arise in other high-level languages.

Disadvantages:

- Steep learning curve: Requires deep understanding of hardware architecture.

- Longer code: For simple tasks, Assembly code is much longer compared to high-level languages.

2. ATmega328P Hardware & Memory Architecture

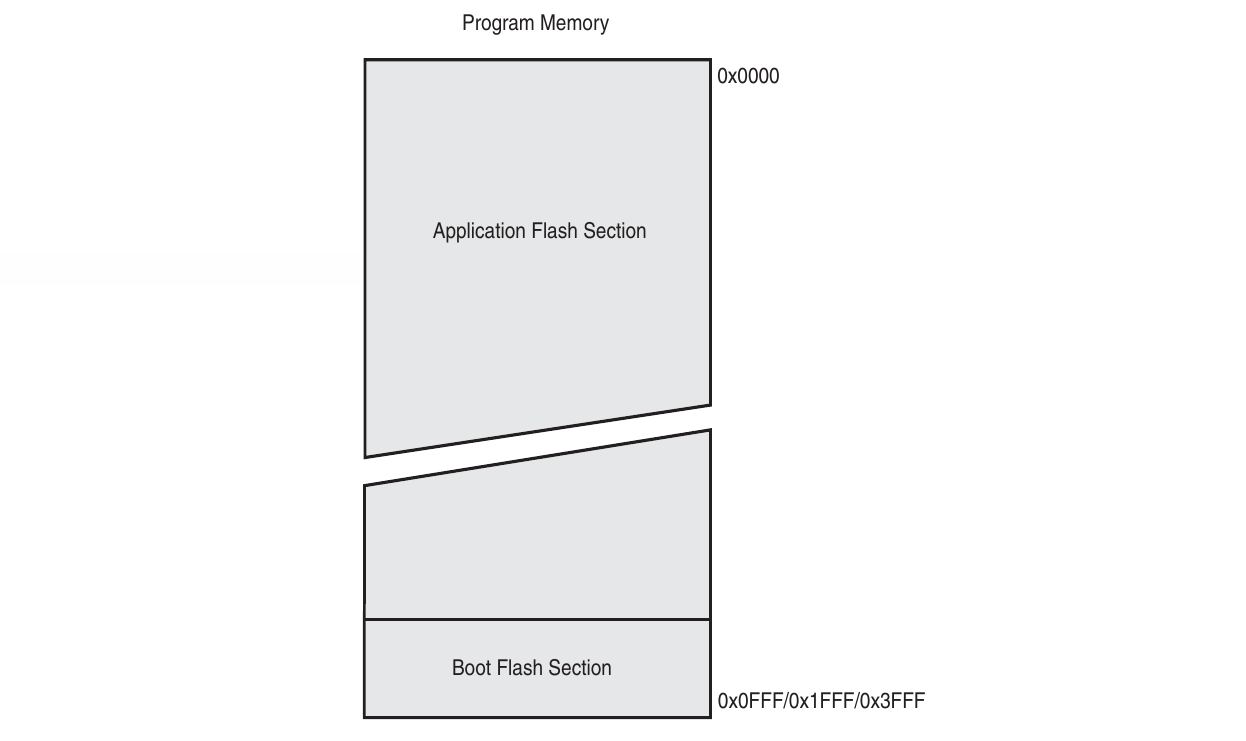

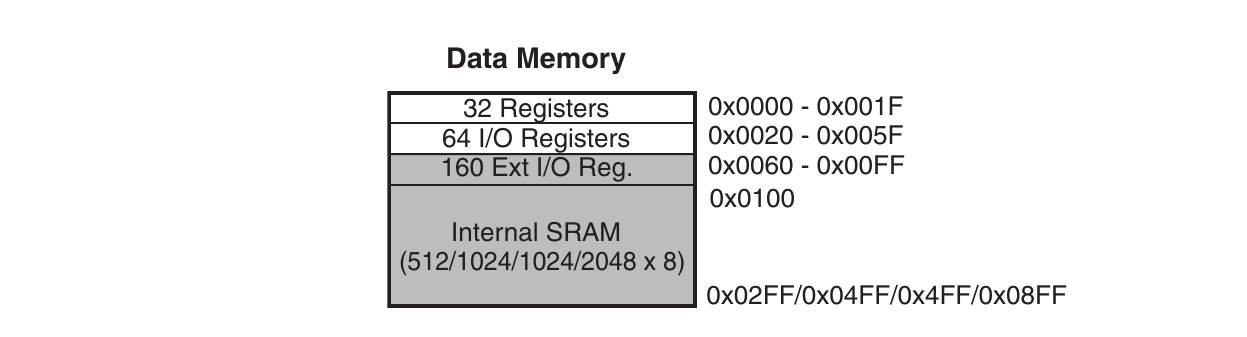

A. Memory Map

The ATmega328P memory map provides information on how the Microcontroller Unit (MCU) uses memory. Here is the address division:

| Category | Address | Size | Description |

|---|---|---|---|

| General Purpose Registers | 0x0000 - 0x001F |

32 x 8 bit | Registers R0 - R31 |

| I/O Registers | 0x0020 - 0x005F |

64 x 8 bit | Accessible via IN/OUT instructions |

| Extended I/O Registers | 0x0060 - 0x00FF |

160 x 8 bit | Additional I/O registers |

| Internal SRAM | 0x0100 - 0x08FF |

2048 x 8 bit | Internal data memory |

B. General Purpose Working Registers (GPR)

The AVR architecture has 32 general-purpose registers labeled R0 through R31. These registers function as temporary storage for data during processing and are directly connected to the ALU (Arithmetic Logic Unit).

Register Division:

| Group | Registers | Characteristics |

|---|---|---|

| Lower Registers | R0 - R15 | Limited functionality. Cannot store immediate values directly (cannot use LDI instruction). |

| Upper Registers | R16 - R31 | More flexible. Can work with immediate data, allowing direct storage of bytes or words. |

Pointer Registers:

The last six registers (R26 through R31) can be combined into 16-bit pointers for indirect memory addressing:

| Pointer Name | Low Register | High Register | Function |

|---|---|---|---|

| X Register | R26 (XL) | R27 (XH) | Pointer for memory access |

| Y Register | R28 (YL) | R29 (YH) | Pointer for memory access |

| Z Register | R30 (ZL) | R31 (ZH) | Pointer for memory & flash access |

3. Input/Output (I/O) Programming

On the Arduino Uno (ATmega328P), digital I/O is controlled through Port B, Port C, and Port D. Each port is 8-bit, allowing control of up to 8 pins simultaneously.

A. Port to Arduino Pin Mapping

| Port | Bits | Arduino Pin | Notes |

|---|---|---|---|

| Port B | PB0 - PB5 | Digital Pin 8 - 13 | PB6-PB7 are used for crystal oscillator |

| Port C | PC0 - PC5 | Analog Pin A0 - A5 | PC6 is the RESET pin |

| Port D | PD0 - PD7 | Digital Pin 0 - 7 | PD0 (RX) and PD1 (TX) for serial communication |

B. Main I/O Registers

Three main registers control the behavior of each port:

| Register | Full Name | Access | Function |

|---|---|---|---|

| DDRx | Data Direction Register | Read/Write | Configures pin direction. 0 = Input, 1 = Output |

| PORTx | Data Register | Read/Write | If Output: Sets logic High (1) or Low (0). If Input: Activates internal Pull-up resistor (1) or Tri-state (0) |

| PINx | Input Pins Address | Read Only | Reads the physical logic state of the pin (0 or 1) |

(Replace 'x' with Port name, e.g., DDRB, PORTB, PINB)

C. Register Bit Configuration Details

DDRx - Data Direction Register

| DDRx Bit Value | Pin Direction | Explanation |

|---|---|---|

| 0 | Input | Pin is configured as input (high impedance) |

| 1 | Output | Pin is configured as output (source/sink current) |

PORTx - Data Register (Depends on DDRx Configuration)

| DDRx | PORTx | Mode | Pin Condition |

|---|---|---|---|

| 0 (Input) | 0 | Tri-state (Hi-Z) | Pin is floating, no pull-up |

| 0 (Input) | 1 | Input Pull-up | Internal pull-up resistor active, pin defaults to HIGH |

| 1 (Output) | 0 | Output Low | Pin outputs 0V (GND) |

| 1 (Output) | 1 | Output High | Pin outputs 5V (VCC) |

PINx - Input Pins Register

| PINx Bit Value | Pin Status | Explanation |

|---|---|---|

| 0 | LOW | Pin voltage is below threshold (near 0V) |

| 1 | HIGH | Pin voltage is above threshold (near 5V) |

4. Assembly Integration with Arduino IDE

To combine Assembly with Arduino C++ code, the extern "C" directive is used in the .ino file and the .global directive is used in the .S (Assembly) file.

File Structure:

.ino File (C/C++):

extern "C" {

void start(); // Declaration of function defined in Assembly

void loop_asm(); // Another function from Assembly

}

void setup() {

start(); // Call Assembly function for initialization

}

void loop() {

loop_asm(); // Call Assembly function for main loop

}

.S File (Assembly):

#define __SFR_OFFSET 0x00

#include "avr/io.h"

.global start

.global loop_asm

start:

SBI DDRB, 5 ; Set PB5 (Pin 13) as Output

RET ; Return to caller

loop_asm:

SBI PORTB, 5 ; Turn on LED

; ... other code

RET

Directive Explanations:

#define __SFR_OFFSET 0x00: Sets the offset for I/O registers to use symbolic names (DDRB, PORTB, etc.).#include "avr/io.h": Includes register definitions for the AVR chip..global: Makes label/function accessible from other files (exported symbol).RET: Instruction to return from subroutine to the calling program.

5. AVR Assembly Instruction Set

Operand Notation

Before diving into the instructions, here are the common operand symbols used:

| Symbol | Description |

|---|---|

| Rd | Destination register (R0-R31). The result of the operation is stored here. |

| Rr | Source register (R0-R31). Used as input for the operation. |

| K | Constant/Immediate value (8-bit: 0-255 or 0x00-0xFF). |

| k | Address constant for SRAM or program memory. |

| A | I/O register address (0-63 for IN/OUT, 0-31 for SBI/CBI). |

| b | Bit number (0-7) within a register or I/O address. |

| X, Y, Z | Pointer registers (X=R27:R26, Y=R29:R28, Z=R31:R30). |

Note: Some instructions only work with upper registers (R16-R31), such as LDI, ANDI, ORI, SUBI, SBCI, and CPI.

A. Data Transfer Instructions

Used to move data between registers or between registers and memory/I/O.

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| LDI | Rd, K | Load Immediate | LDI R16, 0xFF |

Loads 8-bit constant K into register Rd (R16-R31 only) |

| MOV | Rd, Rr | Move/Copy Register | MOV R0, R1 |

Copies contents of register Rr to Rd |

| IN | Rd, A | Input from I/O | IN R16, PINB |

Reads data from I/O port A to register Rd |

| OUT | A, Rr | Output to I/O | OUT PORTB, R16 |

Sends data from register Rr to I/O port A |

| LDS | Rd, k | Load from SRAM | LDS R16, 0x0100 |

Loads data from SRAM address k to register Rd |

| STS | k, Rr | Store to SRAM | STS 0x0100, R16 |

Stores register Rr contents to SRAM address k |

| LD | Rd, X/Y/Z | Load Indirect | LD R16, X |

Loads data from address pointed by pointer X/Y/Z |

| ST | X/Y/Z, Rr | Store Indirect | ST X, R16 |

Stores data to address pointed by pointer X/Y/Z |

| PUSH | Rr | Push to Stack | PUSH R16 |

Saves register to stack |

| POP | Rd | Pop from Stack | POP R16 |

Retrieves data from stack to register |

B. Bit Manipulation Instructions (I/O Specific)

These instructions operate on the lower 32 I/O addresses ($00-$1F). Very efficient for changing one bit without affecting other bits.

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| SBI | A, b | Set Bit in I/O | SBI DDRB, 5 |

Sets bit b in I/O register A to 1 |

| CBI | A, b | Clear Bit in I/O | CBI PORTB, 5 |

Clears bit b in I/O register A to 0 |

| BST | Rr, b | Bit Store to T | BST R16, 3 |

Copies bit b from register Rr to T flag |

| BLD | Rd, b | Bit Load from T | BLD R17, 5 |

Copies T flag to bit b of register Rd |

C. Arithmetic Instructions

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| ADD | Rd, Rr | Add | ADD R1, R2 |

Rd = Rd + Rr |

| ADC | Rd, Rr | Add with Carry | ADC R1, R2 |

Rd = Rd + Rr + C (Carry flag) |

| SUB | Rd, Rr | Subtract | SUB R16, R17 |

Rd = Rd - Rr |

| SBC | Rd, Rr | Subtract with Carry | SBC R16, R17 |

Rd = Rd - Rr - C |

| SUBI | Rd, K | Subtract Immediate | SUBI R16, 10 |

Rd = Rd - K (R16-R31 only) |

| SBCI | Rd, K | Subtract Immediate with Carry | SBCI R17, 0 |

Rd = Rd - K - C |

| INC | Rd | Increment | INC R16 |

Rd = Rd + 1 |

| DEC | Rd | Decrement | DEC R16 |

Rd = Rd - 1 |

| MUL | Rd, Rr | Multiply Unsigned | MUL R16, R17 |

R1:R0 = Rd × Rr (16-bit result) |

| MULS | Rd, Rr | Multiply Signed | MULS R16, R17 |

R1:R0 = Rd × Rr (signed) |

| NEG | Rd | Negate (Two's Complement) | NEG R16 |

Rd = 0x00 - Rd |

D. Logic Instructions

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| AND | Rd, Rr | Logical AND | AND R1, R2 |

Rd = Rd AND Rr |

| ANDI | Rd, K | AND Immediate | ANDI R16, 0x0F |

Rd = Rd AND K (masking) |

| OR | Rd, Rr | Logical OR | OR R1, R2 |

Rd = Rd OR Rr |

| ORI | Rd, K | OR Immediate | ORI R16, 0x80 |

Rd = Rd OR K |

| EOR | Rd, Rr | Exclusive OR | EOR R16, R17 |

Rd = Rd XOR Rr |

| COM | Rd | One's Complement | COM R16 |

Rd = 0xFF - Rd (inverts all bits) |

| CLR | Rd | Clear Register | CLR R16 |

Rd = 0 (same as EOR Rd, Rd) |

| SER | Rd | Set Register | SER R16 |

Rd = 0xFF (R16-R31 only) |

E. Shift & Rotate Instructions

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| LSL | Rd | Logical Shift Left | LSL R16 |

Shift left, bit 0 = 0, bit 7 → Carry |

| LSR | Rd | Logical Shift Right | LSR R16 |

Shift right, bit 7 = 0, bit 0 → Carry |

| ROL | Rd | Rotate Left through Carry | ROL R16 |

Rotate left through Carry flag |

| ROR | Rd | Rotate Right through Carry | ROR R16 |

Rotate right through Carry flag |

| ASR | Rd | Arithmetic Shift Right | ASR R16 |

Shift right, bit 7 remains (preserve sign) |

| SWAP | Rd | Swap Nibbles | SWAP R16 |

Swaps upper and lower 4-bits in register |

F. Branch & Control Flow Instructions

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| RJMP | k | Relative Jump | RJMP loop |

Jump to label k (±2K words) |

| JMP | k | Jump | JMP far_label |

Jump to 22-bit address (all memory) |

| RCALL | k | Relative Call | RCALL delay |

Call subroutine relative to PC |

| CALL | k | Call | CALL far_sub |

Call subroutine at 22-bit address |

| RET | - | Return | RET |

Return from subroutine |

| RETI | - | Return from Interrupt | RETI |

Return from interrupt handler |

| CP | Rd, Rr | Compare | CP R16, R17 |

Compare Rd with Rr (updates flags) |

| CPI | Rd, K | Compare Immediate | CPI R16, 5 |

Compare Rd with constant K |

| CPC | Rd, Rr | Compare with Carry | CPC R17, R19 |

For multi-byte comparison |

| BREQ | k | Branch if Equal | BREQ target |

Jump if Z flag = 1 (result equal) |

| BRNE | k | Branch if Not Equal | BRNE loop |

Jump if Z flag = 0 (result not equal) |

| BRLO | k | Branch if Lower | BRLO less |

Jump if C flag = 1 (unsigned <) |

| BRSH | k | Branch if Same or Higher | BRSH greater |

Jump if C flag = 0 (unsigned ≥) |

| BRLT | k | Branch if Less Than | BRLT neg |

Jump if S flag = 1 (signed <) |

| BRGE | k | Branch if Greater or Equal | BRGE pos |

Jump if S flag = 0 (signed ≥) |

G. Skip Instructions

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| SBIS | A, b | Skip if Bit in I/O Set | SBIS PINB, 0 |

Skip next instruction if bit = 1 |

| SBIC | A, b | Skip if Bit in I/O Cleared | SBIC PIND, 2 |

Skip next instruction if bit = 0 |

| SBRS | Rr, b | Skip if Bit in Register Set | SBRS R16, 7 |

Skip if bit b in register = 1 |

| SBRC | Rr, b | Skip if Bit in Register Cleared | SBRC R16, 0 |

Skip if bit b in register = 0 |

H. Other Instructions

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| NOP | - | No Operation | NOP |

Does nothing (1 clock cycle) |

| SLEEP | - | Sleep | SLEEP |

Enters sleep mode (power saving) |

| WDR | - | Watchdog Reset | WDR |

Resets watchdog timer |

| SBIW | Rd, K | Subtract Immediate from Word | SBIW R24, 1 |

Subtract K from 16-bit value (R25:R24) |

| ADIW | Rd, K | Add Immediate to Word | ADIW R24, 1 |

Add K to 16-bit value |

6. Status Register (SREG)

The Status Register contains flags that indicate the results of arithmetic/logic operations. This register is crucial for branch instructions.

| Bit | Name | Description |

|---|---|---|

| 7 | I (Global Interrupt Enable) | Enables/disables global interrupts |

| 6 | T (Bit Copy Storage) | Storage for BLD/BST instructions |

| 5 | H (Half Carry Flag) | Carry from bit 3 to bit 4 (for BCD) |

| 4 | S (Sign Flag) | S = N ⊕ V (for signed operations) |

| 3 | V (Overflow Flag) | Two's complement overflow |

| 2 | N (Negative Flag) | Result is negative (bit 7 = 1) |

| 1 | Z (Zero Flag) | Result = 0 |

| 0 | C (Carry Flag) | Carry/borrow from operation |

7. Delay Implementation Without Library

Delays can be created using nested loops that consume a certain number of clock cycles.

Delay Calculation Concept:

- ATmega328P on Arduino Uno runs at 16 MHz (16 million clock cycles per second)

- 1 millisecond = 16,000 clock cycles

DECinstruction takes 1 cycle,BRNEtakes 2 cycles (if branch taken)

Delay Implementation Examples:

; Delay approximately 1 second (with nested loop)

delay_1s:

LDI R18, 64 ; Outer counter

outer_loop:

LDI R24, lo8(62500) ; Inner counter low byte

LDI R25, hi8(62500) ; Inner counter high byte

inner_loop:

SBIW R24, 1 ; Subtract 16-bit counter (2 cycles)

BRNE inner_loop ; Loop if not 0 (2 cycles if taken)

DEC R18 ; Subtract outer counter

BRNE outer_loop ; Loop outer if not 0

RET

; Simple delay with single loop

delay_simple:

LDI R16, 255 ; Load counter

delay_loop:

DEC R16 ; Decrement counter (1 cycle)

BRNE delay_loop ; Branch if not zero (2 cycles)

RET ; Return (approximately 765 cycles total)

8. Complete Program Examples

A. Blink LED

#define __SFR_OFFSET 0x00

#include "avr/io.h"

.global main

main:

SBI DDRB, 5 ; Set PB5 (Pin 13) as Output

loop:

SBI PORTB, 5 ; Turn on LED (Output HIGH)

RCALL delay ; Call delay subroutine

CBI PORTB, 5 ; Turn off LED (Output LOW)

RCALL delay ; Call delay subroutine

RJMP loop ; Repeat continuously

delay:

LDI R18, 82 ; Outer loop counter

outer:

LDI R24, lo8(60000) ; Inner loop counter (low byte)

LDI R25, hi8(60000) ; Inner loop counter (high byte)

inner:

SBIW R24, 1 ; Subtract word (R25:R24)

BRNE inner ; Loop if not 0

DEC R18 ; Subtract outer counter

BRNE outer ; Loop outer if not 0

RET ; Return to caller

B. Reading Button and Controlling LED

#define __SFR_OFFSET 0x00

#include "avr/io.h"

.global main

main:

; Setup

SBI DDRB, 5 ; PB5 (Pin 13) as Output (LED)

CBI DDRD, 2 ; PD2 (Pin 2) as Input (Button)

SBI PORTD, 2 ; Activate Pull-up on PD2

loop:

SBIC PIND, 2 ; Skip next instruction if button pressed (LOW)

RJMP led_off ; If not pressed, turn off LED

led_on:

SBI PORTB, 5 ; Turn on LED

RJMP loop ; Return to loop

led_off:

CBI PORTB, 5 ; Turn off LED

RJMP loop ; Return to loop

C. Toggle LED with Button (Simple Debounce)

#define __SFR_OFFSET 0x00

#include "avr/io.h"

.global main

main:

; Initialization

SBI DDRB, 5 ; PB5 as Output (LED)

CBI DDRD, 2 ; PD2 as Input (Button)

SBI PORTD, 2 ; Activate internal Pull-up

CLR R20 ; R20 = LED status (0 = off)

wait_press:

SBIC PIND, 2 ; Wait for button pressed (LOW)

RJMP wait_press

; Button pressed - toggle LED

SBRC R20, 0 ; Skip if bit 0 of R20 = 0 (LED off)

RJMP turn_off

turn_on:

SBI PORTB, 5 ; Turn on LED

LDI R20, 1 ; Set status = on

RJMP debounce

turn_off:

CBI PORTB, 5 ; Turn off LED

CLR R20 ; Set status = off

debounce:

RCALL delay ; Delay for debounce

wait_release:

SBIS PIND, 2 ; Wait for button released (HIGH)

RJMP wait_release

RCALL delay ; Delay debounce after release

RJMP wait_press ; Return to wait for press

delay:

LDI R18, 50

d_outer:

LDI R24, lo8(10000)

LDI R25, hi8(10000)

d_inner:

SBIW R24, 1

BRNE d_inner

DEC R18

BRNE d_outer

RET

Module 3 - Serial Port

Introduction to USART

1. USART Definition

USART (Universal Synchronous/Asynchronous Receiver/Transmitter) is a communication protocol used to transfer data between electronic devices, such as microcontrollers, sensors, and other components. This protocol is highly flexible as it supports two main modes:

- Synchronous

- Asynchronous

2. UART vs. USART

While often used interchangeably, there is a technical difference:

- UART (Universal Asynchronous Receiver/Transmitter): Supports only asynchronous communication. It requires no clock signal as it relies on start/stop bits and pre-defined baud rates.

- USART (Universal Synchronous/Asynchronous Receiver/Transmitter): A superset of UART. It supports both asynchronous and synchronous modes. In synchronous mode, a dedicated clock pin (XCK) is used to synchronize data.

3. Operating Modes

A. Asynchronous Mode

In this mode, the USART module transmits data without an external clock signal. Synchronization is achieved using data frames consisting of:

- Start Bit: Indicates the beginning of transmission.

- Data Bits: Contains the primary information (typically 5-9 bits).

- Parity Bit (Optional): Used for error detection (Even, Odd, or None).

- Stop Bit: Indicates the end of transmission.

Characteristics: Suitable for long-distance communication or between devices that do not share the same clock.

B. Synchronous Mode

Uses a clock signal to synchronize data transfer between the transmitter and the receiver.

- Requires the same clock configuration on both devices.

- Allows for faster and more reliable data transfer compared to asynchronous mode.

Characteristics: Ideal for multimedia applications or high-speed bulk data transfers.

4. Configuration and Baud Rate

To use USART, several parameters must be defined:

- Baud Rate: The speed of data transmission (bits per second).

- Data Format: The number of data bits, parity, and stop bits.

- Interrupt: Enables notifications when data is finished being sent or received.

5. USART and Arduino Serial Monitor

In the Arduino ecosystem (such as the Uno), the USART peripheral is the primary way the microcontroller communicates with your computer:

- Hardware Connection: The ATmega328P uses its USART pins (TX on Pin 1, RX on Pin 0). These are connected to an onboard USB-to-Serial converter chip.

- Serial Monitor: When you open the Serial Monitor or Serial Plotter in the Arduino IDE, it acts as the "Receiver" (RX) for data sent by the Arduino and the "Transmitter" (TX) for data you type in.

- Baud Rate Alignment: For communication to work, the baud rate selected in the Serial Monitor (e.g., 9600) must match the baud rate configured in your code. If they do not match, you will see "garbage" characters or no data at all.

In Proteus, follow these steps to simulate using a Virtual Terminal to mimic Serial Monitor functionality:

- Click on Virtual Instruments Mode in the left sidebar.

- Select the Virtual Terminal component and place it on the schematic.

- Add an Arduino Uno to your schematic. Then, connect the TX and RX pins of the Virtual Terminal to the RX and TX pins of the Arduino Uno respectively.

- Double-click on the Virtual Terminal to set the Baud Rate (e.g., 9600) to match your code.

Baud Rate Calculation Formula (UBRR)

The UBRR (USART Baud Rate Register) value is calculated based on the CPU clock frequency (F_CPU) and the desired Baud Rate:

UBRR = (F_CPU / (16 * BAUD)) - 1

Calculation Example:

If F_CPU = 16 MHz and the target BAUD = 9600 bps:

- UBRR = (16,000,000 / (16 * 9600)) - 1

- UBRR = 104.16 - 1

- UBRR ≈ 103 (Hex: 0x67)

USART Register Architecture of ATmega328p

The ATmega328p microcontroller uses several specific registers to control and monitor USART communication.

1. UBRR (USART Baud Rate Register)

A 16-bit register that determines the communication speed. It is divided into two 8-bit registers:

- UBRR0H: Stores the 8 most significant bits (MSB).

- UBRR0L: Stores the 8 least significant bits (LSB).

The following table provides a reference for UBRR0 (USART Baud Rate Register) settings corresponding to standard baud rates (bps). It details the required register values for three common oscillator frequencies (f_osc): 16.0000 MHz, 18.4320 MHz, and 20.0000 MHz. For each frequency, the table accounts for both normal speed (U2Xn = 0) and double speed (U2Xn = 1) modes, including the resulting percentage error for each configuration.

2. UDR (USART Data Register)

An 8-bit register that serves a dual purpose:

- TXB (Transmit Data Buffer): The location where data to be sent is written.

- RXB (Receive Data Buffer): The location where incoming data is read.

3. UCSR0A (USART Control and Status Register A)

Used to monitor communication status and configure the speed mode.

| Bit | Name | Description |

|---|---|---|

| RXC0 | Receive Complete | Set to 1 if there is new unread data in the UDR. |

| TXC0 | Transmit Complete | Set to 1 if all data has been transmitted. |

| UDRE0 | UDR Empty | Set to 1 if the UDR register is empty and ready for new data. |

| FE0 | Frame Error | Occurs when there is an error in the stop bit. |

| DOR0 | Data Overrun | Occurs when new data arrives before old data is read. |

| UPE0 | Parity Error | Occurs when there is a parity error in the received data. |

| U2X0 | Double Speed | If set to 1, the transmission speed is doubled. |

| MPCM0 | Multi-processor | Enables multi-processor communication mode. |

4. UCSR0B (USART Control and Status Register B)

Used to enable the module and interrupts.

- RXCIE0: Enables the receive complete interrupt.

- TXCIE0: Enables the transmit complete interrupt.

- UDRIE0: Enables the data register empty interrupt.

- RXEN0: Enables the Receiver.

- TXEN0: Enables the Transmitter.

- UCSZ02: Additional bit (along with UCSR0C) to determine data size (5-9 bits).

- RXB80 / TXB80: Holds the 9th data bit (if using 9-bit format).

5. UCSR0C (USART Control and Status Register C)

Used for frame format configuration and operating mode.

- UMSEL01:0: Selects the mode (Asynchronous or Synchronous).

- UPM01:0: Selects the Parity mode (None, Even, or Odd).

- USBS0: Selects the number of Stop Bits (1 or 2).

- UCSZ01:0: Determines the data size (paired with UCSZ02 in UCSR0B).

- UCPOL0: Clock polarity for synchronous mode.

Note: When writing to UCSR0C, ensure bit configurations are performed carefully according to the communication protocol requirements of the target device.

Implementation and Assembly Code Examples

This page contains basic implementation examples of USART serial communication using the Assembly programming language on an AVR Microcontroller (ATmega328p).

1. Printing Text to Serial Monitor

This code is used to repeatedly send the string "Programming Serial Interface!" to the Serial Monitor via the USART port.

;------------------------

; Assembly Code - Print Text

;------------------------

#define __SFR_OFFSET 0x00

#include "avr/io.h"

;------------------------

.global main

main:

CLR R24

STS UCSR0A, R24 ; Clear UCSR0A register

STS UBRR0H, R24 ; Clear UBRR0H

LDI R24, 103 ; Set UBRR value = 103 (9600 Baud Rate)

STS UBRR0L, R24

LDI R24, (1<<RXEN0) | (1<<TXEN0) ; Enable RX and TX

STS UCSR0B, R24

LDI R24, (1<<UCSZ00) | (1<<UCSZ01) ; Mode: 8-bit data, 1 stop bit, No Parity

STS UCSR0C, R24

print_msg:

LDI R30, lo8(message)

LDI R31, hi8(message) ; Z points to string message

agn:

LPM R18, Z+ ; Load character into R18

CPI R18, 0 ; Check if end of string (null)

BREQ ext ; If yes, exit loop

l1:

LDS R17, UCSR0A

SBRS R17, UDRE0 ; Wait until buffer is empty (UDRE0=1)

RJMP l1

STS UDR0, R18 ; Send character to Serial Monitor

RJMP agn ; Loop to next character

ext:

RCALL delay_sec ; Wait for a moment

RJMP print_msg ; Repeat string transmission

message:

.ascii "Programming Serial Interface!"

.byte 10, 13, 0

delay_sec: ; Delay Subroutine (~3 seconds)

LDI R20, 255

l4: LDI R21, 255

l5: LDI R22, 255

l6: DEC R22

BRNE l6

DEC R21

BRNE l5

DEC R20

BRNE l4

RET

2. Reading Input from Serial Monitor

This code reads characters sent from the Serial Monitor and controls an LED. If the character 'H' is received, the LED turns ON; if 'L' is received, the LED turns OFF.

;------------------------

; Assembly Code - Input Text and Control LED

;------------------------

#define __SFR_OFFSET 0x00

#include "avr/io.h"

;------------------------

.global main

main:

CLR R24

STS UBRR0H, R24

LDI R24, 103

STS UBRR0L, R24

LDI R24, (1<<RXEN0 | 1<<TXEN0)

STS UCSR0B, R24

LDI R24, (1<<UCSZ01 | 1<<UCSZ00)

STS UCSR0C, R24

SBI DDRB, 5 ; Set PB5 as output

wait_input:

; 1. Check if a byte arrived

LDS R17, UCSR0A

SBRS R17, RXC0 ; Wait for Receive Complete

RJMP wait_input

; 2. Read the character into R18

LDS R18, UDR0

; 3. Check if character is 'H'

CPI R18, 'H'

BREQ led_on

; 4. Check if character is 'L'

CPI R18, 'L'

BREQ led_off

RJMP wait_input

led_on:

SBI PORTB, 5 ; Turn LED ON

RJMP wait_input

led_off:

CBI PORTB, 5 ; Turn LED OFF

RJMP wait_input

Module 4 - Arithmetic

From memory access, addressing modes, the SREG, to arithmetic operations in AVR assembly,

1. Memory in AVR Architecture

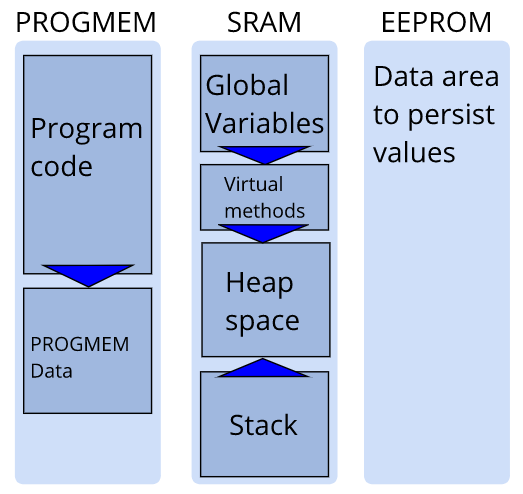

AVR Architecture is an 8 bit single-chip RISC microcontroller with a modified Harvard Architecture that is organized as the following which causes it to behave certain ways when handling memory.

You don't have to memorize all this don't worry.

There are several memory spaces in this organization, but for now we will look at the two most important ones to know.

Program/Flash Memory

When you compile and upload codes (flashing), it's stored in the Flash Memory section semi-permanently. During runtime, the control unit fetches instructions from this memory section.

When you compile and upload codes (flashing), it's stored in the Flash Memory section semi-permanently. During runtime, the control unit fetches instructions from this memory section.

This portion of the memory is non-volatile which means the data stored won't be erased after power loss.

Data Memory - DS (Data Space)

The Data Memory consists of several memory parts mapped into one contiguous memory addresses.

The Data Memory consists of several memory parts mapped into one contiguous memory addresses.

- 32 General Purpose Registers (0x0000 - 0x001F)

- 64 I/O Registers (0x0020 - 0x005F)

- 160 Extended I/O Registers (0x0060 - 0x00FF)

- SRAM (Implementation Spesific)

The Static RAM (SRAM) is a memory block used to store data used during runtime. One part of this is the stack that may come in handy for temporary data (more on this later).

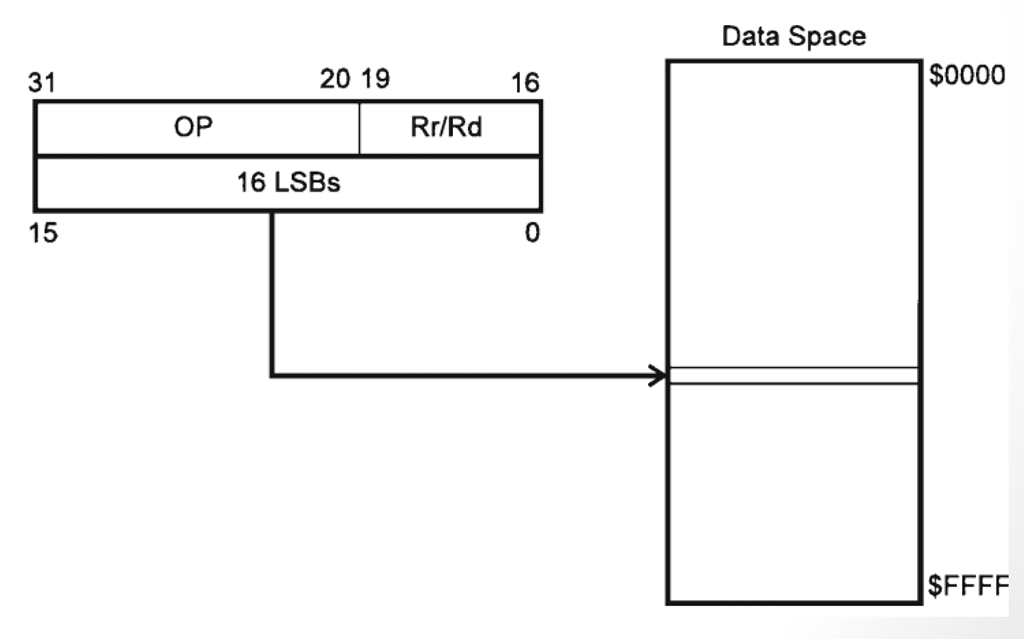

2. Addressing Modes

Due to how the AVR Architecture and its memory are organized, AVR instructions, including arithmetic instructions, must follow certain addressing methods. Addressing methods are how the control unit may access different data locations according to the instruction which are usually 16 - 32 bits in length. Those data locations may include general purpose registers, I/O registers, extended I/O registers, and the SRAM.

Single Register Direct (Rd)

Operates on a single general purpose register Rd with d being values 0 - 31 (R0 - R31). Data is read from the register Rd, operated on, then stored back into the same register.

Some instructions with this addressing mode are ROL Rd and COM Rd which rotates the bits in Rd and inverts the bits in Rd respectively.

Double Register Direct (Rd, Rr)

Unlike Single Register Direct, Double Register Direct operates on two general purpose registers: source Rr and destination Rd. Data is read from Rr which are then operated alongside Rd to be stored back into Rd.

Instructions such as ADD Rd, Rr and AND Rd, Rr operates on both Rd and Rr which then stores the results (Addition and bitwise AND) in Rd.

Immediate Mode (Rd, K)

A constant value K alongside a register Rd is provided in the instruction itself, therefore the data itself is stored as a constant inside the Flash Memory. The constant value is limited to 255 (0xFF, 8 bits) and the register used is limited to R16 - R31 (4 bits with an offset).

Instructions such as ORI Rd, K and LDI Rd, K operates with a constant value K then storing it into Rd (bitwise OR and Loading).

Notice how the instructions have 'I' in its names (stands for Immediate).

Some instructions that have W (Word) in its name operates on 16 bit words which are stored in two consecutive registers R[d + 1]:Rd. One instruction that operates like this is the ADIW Rd, K that adds a constant K to the 16 bit data in R[d + 1]:Rd. Word Immediate instructions can only operate on 4 even-indexed GP registers {R24, R26, R28, R30} and are limited to 6 bits constant values (0 - 63).

The 16 bit opcode for ADIW is [1001 0110 KKdd KKK] which limits K to 6 bits and d to 2 bits (4 different registers max).

I/O Direct (Rd/Rr, A)

Operates with I/O memory address A. Headers like avr/io.h defines these memory addresses into readable constants such as PORTB, PINC, and 'DDRA'. This doesn't include Extended I/O addresses such as UBBR0H.

Instructions such as IN Rd, A and OUT A, Rr stores IO(A) into Rd and Rr into IO(A) respectively.

Data Direct (Rd/Rr, k)

Instructions with this addressing utilizes 16 bit value k (0 - 65535) which is an address that corresponds to a space in memory, including the Extended I/O addresses scuh as UBRR0H and UCSR0A.

One instruction with Data Direct addressing is LDS Rd, k which loads the value in address k to register Rd.

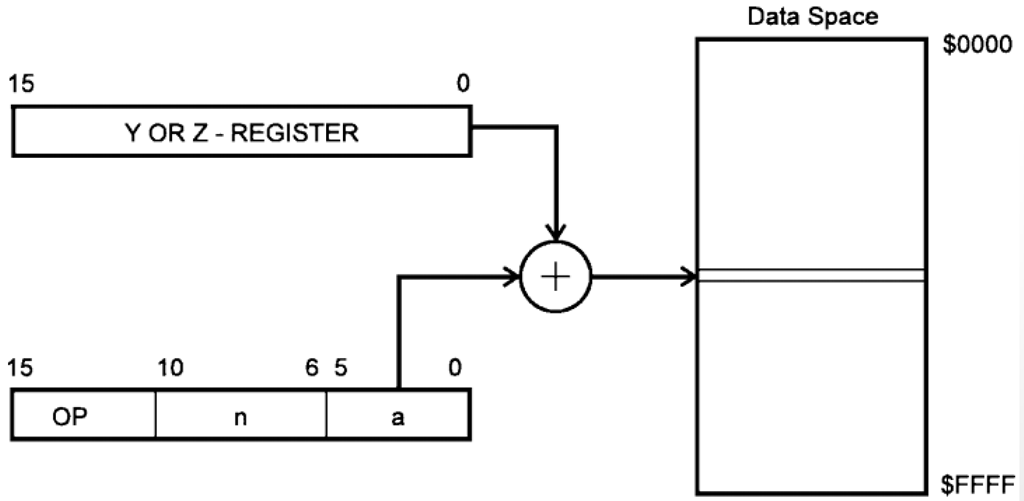

Data Indirect (Rd/Rr, X/Y/Z +/- q)

Registers X, Y, and Z corresponds to certain 16 bit register pairs in the memory.

| Register | Higher Byte | Lower Byte |

|---|---|---|

| X | R27 | R26 |

| Y | R29 | R28 |

| Z | R31 | R30 |

Instructions with Data Indirect addressing operates on data stored in the address stored in the X/Y/Z registers. For example, if X contains the value 0x01FF, then LD Rd, X would load the data value stored in address 0x01FF into Rd.

A feature of Data Indirect addressing is pre/post increment/decrement operators. By adding '+' or '-' next to the X/Y/Z register (eg: X+), the address stored would be automatically incremented or decremented respectively. This operation can be pre-ordered or post-ordered meaning the address value change would happen before or after the instruction itself.

As an example, assume Y = 0x02. Instruction LD Rd, Y+ would store the value DS(Y) into Rd THEN increments Y to be 0x03. As opposed to this, putting the increment operator before Y (LD Rd, +Y) would first increment the value of Y to be 0x03 THEN loads the data in the newly updated address into Rd.

This may come in handy when operating with arrays stored as blocks of consecutive memory.

Certain instructions also allows accessing memory with displacement q on pointer registers Y/Z (X gak diajak). These instructions, usually ending with D, such as STD Y+3, Rd would offset the address stored in Y by 3 which stores the value in Rd into address DS(Y+3).

To see which instructions uses which memory addressing methods, refer to the AVR Instruction Set Manual. Knowing which instructions utilizes which memory addressing method would help you choose the best instruction to use in different situations when handling arithmetic and logic operations.

3. The Status Register

The Status Register (SREG) is a special 8 bit register that saves different operational status flags in each bit. Different operations may affect different flags (bit) of the register which then would be useful to create decisions after.

In AVR architecture, SREG is an I/O register meaning that it can be operated with instructions such as OUT and IN.

Carry Flag (C) [0]

- Indicates a Carry after addition or a Borrow after substraction.

- Usually happens when adding up numbers that results in a result greater than 8 bits (255) or when substracting numbers that results a negative analytically.

- Substracting a smaller number by a bigger one would result to a negative. This can be used to test whether a number is smaller than the other.

Zero Flag (Z) [1]

- Indicates that the previous operation results a 0.

- Can be set by different arithmetic operations such as

SUBorDECto logical operations such asAND. - Substracting two equal values would result in a 0. This property can be used to test if two numbers are equal.

Negative Flag (N) [2]

- Indicates that the previous number results a negative.

- Under the hood works by testing the most significant bit (bit 7, leftmost) which indicates a 2s complement.

Two's Complement Overflow Flag (V) [3]

- Indicates that the previous operation is outside the range of signed values -128 to 127. These two values are the lowest and highest 8 bit signed values.

- Useful for testing overflow during signed 8 bit integer operations.

Sign Flag (S) [4]

- XOR of N and V flag.

- Indicates the sign of the result of the last operation. S = 1 means the last operation resulted in a negative signed number.

Half Carry (H) [5]

- Functions like the Carry flag but for only the lower nibbles of the last operation.

- Can come in handy when operating with 4 bit values such as BCD.

Bit Copy Storage (T) [6]

- Unlike the others, can be freely used by the programmer anyway they like.

- Set to 1 with

SETand 0 withCLTinstructions. - Can be used by other registers with

BST Rr, bandBLD Rd, bthat moves the 1 bit value of T into or out of bit b of register Rr/Rd. - Technically a free 1 bit storage.

Global Interrupt Enable (I) [7]

- Enables interrupt when set to 1 with

SEIor disables it when cleared withCLI.

4. Advanced Arithmetic Operations

As a refresher, here are some fundamental AVR arithmetic and logical instructions.

| Mnemonic | Operand | Description | Example | Notes |

|---|---|---|---|---|

| ADD | Rd, Rr | Add | ADD R1, R2 |

Rd = Rd + Rr |

| ADC | Rd, Rr | Add with Carry | ADC R1, R2 |

Rd = Rd + Rr + C (Carry flag) |

| ADIW | Rd, K | Add Immediate to Word | ADIW R24, 40 |

R[d+1]:Rd = R[d+1]:Rd + K |

| SUB | Rd, Rr | Subtract | SUB R16, R17 |

Rd = Rd - Rr |

| SBC | Rd, Rr | Subtract with Carry | SBC R16, R17 |

Rd = Rd - Rr - C |

| SUBI | Rd, K | Subtract Immediate | SUBI R16, 67 |

Rd = Rd - K |

| SBIW | Rd, K | Substract Immediate from Word | SBIW R24, 40 |

R[d+1]:Rd = R[d+1]:Rd - K |

| SBCI | Rd, K | Subtract Immediate with Carry | SBCI R17, 0 |

Rd = Rd - K - C |

| INC | Rd | Increment | INC R16 |

Rd = Rd + 1 |

| DEC | Rd | Decrement | DEC R16 |

Rd = Rd - 1 |

| MUL | Rd, Rr | Multiply Unsigned | MUL R16, R17 |

R1:R0 = Rd × Rr (16-bit result) |

| MULS | Rd, Rr | Multiply Signed | MULS R16, R17 |

R1:R0 = Rd × Rr (signed) |

| NEG | Rd | Negate (Two's Complement) | NEG R16 |

Rd = 0x00 - Rd |

| AND | Rd, Rr | Logical AND | AND R1, R2 |

Rd = Rd AND Rr |

| ANDI | Rd, K | AND Immediate | ANDI R16, 0x0F |

Rd = Rd AND K |

| OR | Rd, Rr | Logical OR | OR R1, R2 |

Rd = Rd OR Rr |

| ORI | Rd, K | OR Immediate | ORI R16, 0x80 |

Rd = Rd OR K |

| EOR | Rd, Rr | Exclusive OR | EOR R16, R17 |

Rd = Rd XOR Rr |

| COM | Rd | One's Complement | COM R16 |

Rd = 0xFF - Rd (inverts all bits) |

| NEG | Rd | Two's Complement | NEG R16 |

Rd = -Rd (Signed) |

| CLR | Rd | Clear Register | CLR R16 |

Rd = 0 |

| SER | Rd | Set Register | SER R16 |

Rd = 0xFF (R16-R31 only) |

Register Pair Arithmetic

To perform arithmetic operations with 16 bit words (0 - 65535), we can utilize the Carry Flag to perform ripple carry arithmetic operations.

16 Bit Word Addition

Suppose you want to add two big 16 bit numbers 26983 and 4882 stored in two register pairs R16:R17 and R18:R19. You can add the lower byte first then add the higher byte with a carry addition.

; DEC 26983 = HEX 0x6967

LDI R16, 0x69 ; upper byte

LDI R17, 0x67 ; lower byte

; DEC 4882 = HEX 0x1312

LDI R18, 0x13 ; upper byte

LDI R19, 0x12 ; lower byte

ADD R17, R19 ; add lower byte

ADC R16, R18 ; add upper byte + carry from lower

; R16:R17 = 31865

16 Bit Word Substraction

A similar thing can be done for substracting two 16 bit numbers.

; DEC 26983 = HEX 0x6967

LDI R16, 0x69 ; upper byte

LDI R17, 0x67 ; lower byte

; DEC 4882 = HEX 0x1312

LDI R18, 0x13 ; upper byte

LDI R19, 0x12 ; lower byte

SUB R17, R19 ; substract lower byte

SBC R16, R18 ; substract upper byte - borrow (C) from lower

; R16:R17 = 22101

Immediate Arithmetic

There are 3 immediate arithmetic instructions: ADIW, SBIW, and SUBI. In AVR there is no "Add with immediate" instruction. To do so, you can utilize the SUBI Rd, K instruction to substract a negative immediate number to achieve addition.

Suppose you want to add 67 to 61 stored in R16. You can do the following

LDI R16, 61

SUBI R16, -67 ; - -61 = + 61

; R16 = 128

Notice how there are only immediate instructions for word addition and substraction? Recall that word immediate addressing (ADIW & SBIW) can only operate on 6 bit values (0 - 63). How can we perform immediate arithmetic operations on bigger numbers like 26983?

Word Immediate Arithmetic

To perform addition/substraction operation with immediate numbers greater than 63, we simply split the word operation into two byte immediate operations similar to the previously explained 16 bit operations.

16 Bit Immediate Addition

; DEC 4882 = HEX 0x1312

LDI R16, 0x13 ; upper byte

LDI R17, 0x12 ; lower byte

.EQU num, 0x5457 ; immediate constant DEC 21591

SUBI R17, lo8(-num) ; 0x12 - -0x57 = 0x12 + 0x57 ; add lower byte

SBCI R16, hi8(-num) ; 0x13 - -0x54 - C = 0x13 + 0x54 + C ; add upper byte

; R16:R17 = 26473

16 Bit Immediate Substraction

LDI R16, 0x67 ; yeah you get the idea atp

LDI R17, 0x69

.EQU num, 0x1312

SUBI R17, lo8(num) ; this time we simply just substract it

SBCI R16, hi8(num) ; no need to be negative :)

; R16:R17 = 26983

Multiplying Numbers

There are multiple multiplication instructions in AVR, each supporting different data formats such as MUL Rd, Rr for unsigned numbers, MULS Rd, Rr for signed numbers, and MULSU Rd, Rr for multiplying a signed with an unsigned number.

Generally, the way they behave are similar: they multiply Rd with Rr then storing a 16 bit result in R1:R0.

LDI R16, 23

LDI R17, 9

MUL R16, R17

; R1:R0 = 23 * 9 = 207 (16 bits wide)

5. The Stack

The Stack is a memory section of the SRAM that follows First-In-First-Out (FIFO) principles. It is generally used to store temporary data for quick and easy access.

The top of the stack is tracked by the 16 bit (adjusting to memory addressing) Stack Pointer that stores the address. It increments and decrements accordingly.

The stack grows downwards meaning that newer data is placed on lower memory address.

The top, is in fact, the bottom

The stack is used during subroutine (think of functions) calling to store the previous program counter when called with RCALL or ICALL. The program then restores the program counter to return to the previous location with RET.

Aside from subroutines, you can utilize the stack for your own use. The following are instructions that affects the stack.

| Instruction | Stack Pointer | Description |

|---|---|---|

| PUSH Rd | SP = SP - 1 | Value in Rd is pushed onto the top of the stack. |

| POP Rr | SP = SP + 1 | The top of the stack is popped into Rr |

| RCALL ICALL | SP = SP - 2 | PC is stored onto the stack. Program jumps to the subroutine. |

| RET RETI | SP = SP + 2 | The top of the stack is popped back into PC. The program returns to the caller address. |

Push Operation

Pop Operation

Using Stacks

A very useful use case for stacks is as temporary storage without using up temporary registers to reduce mental overhead. For example, you might swap the contents of two registers R16 and R17.

PUSH R16 ; temporarily store R16

MOV R16, R17 ; overwrite R16 with R17

POP R17 ; return the temporary data to R17

This form of temporary container may become handy as your program grows. Even though AVR provides 32 general purpose registers, keeping track each and every single one of them may become harder as your program grows with more subroutines. One subroutine might unintentionally modify a register that you were using during its execution which might produce unexpected results.

For example, given a subroutine that interact with USART using R24

SER_send_byte:

LDS R24, UCSR0A ; R24 is filled with the content of UCSR0A

SBRS R24, UDRE0

...

RET

Calling it from main would unexpectedly modify R24

main:

LDI R24, 0b00001010

...

RCALL SER_send_byte

OUT TCCR0B, R24 ; this behaviour might be unexpected since R24 is no longer the same

Aside from giving proper documentations to subroutines which provides information on affected registers, the stack can be used to store values in affected register and retrieve it before returning.

; Sends R16 to USART

; Blocks while UDRE0 is not ready.

; Registers Affected: R24

SER_send_byte:

PUSH R24 ; stores R24

LDS R24, UCSR0A

SBRS R24, UDRE0

RJMP SER_send_byte

STS UDR0, R16

POP R24 ; retrieve the value back to R24

RET

Do keep in mind that this would add an overhead by using additional cycles and memory for storing into the stack.

6. Printing Bytes as Hexadecimal Values

To easily debug and view numbers, we can create a subroutine that outputs numbers into serial. Since our architecture uses 8 bits, it is easier to print bytes as two hexadecimal values 0x00 - 0xFF by splitting the upper and lower nibbles. In this page, we will create a subroutine that prints R16 as hexadecimal to serial.

Given the following subroutines to use the serial:

; Initializes USART

; Registers Affected: R24

SER_init:

CLR R24

STS UCSR0A, R24 ; clear UCSR0A register

STS UBRR0H, R24 ; clear UBRR0H register

LDI R24, 103 ; store in UBRR0L 103 value

STS UBRR0L, R24 ; to set baud rate 9600

LDI R24, 1 << RXEN0 | 1 << TXEN0 ; enable RXB & TXB

STS UCSR0B, R24

LDI R24, 1 << UCSZ00 | 1 << UCSZ01 ; asynch, no parity, 1 stop, 8 bits

STS UCSR0C, R24

RET

; Prints character in R16 to USART

; Blocks while UDRE0 is not ready.

; Registers Affected: R24

SER_send_byte:

LDS R24, UCSR0A

SBRS R24, UDRE0 ; test data buffer if data can be sent

RJMP SER_send_byte ; loop back if not ready

STS UDR0, R16 ; sends R16 to USART

RET

Printing Nibbles

A 4 bit nibble, the lower parts of a byte, can be mapped into hexadecimal values 0 - F. Adding '0' to the nibble would map values 0 - 9 to its respective '0' - '9' ASCII characters.

SER_nibble:

ANDI R16, 0x0F ; mask that removes the higher nibble

SUBI R16, -'0' ; add '0' to R16 to represent ASCII '0' - '9'.

...

Just simply doing this, however, wouldn't work on values A - F since they are not continuously mapped right after '9' which would instead prints ':' for 10. To do so, we can check whether the resulting ASCII is greater than '9'. If so, we can then add it by 7 since 'A' is located 7 characters after '9'.

SER_nibble:

PUSH R16 ; preserves R16

ANDI R16, 0x0F ; mask that removes the higher nibble

SUBI R16, -'0' ; add '0' to R16 to represent ASCII '0' - '9'.

CPI R16, '9' + 1 ; compare with '9' + 1 = ':'

BRLT print_nibble ; if no problem just simply print the character

SUBI R16, -7 ; otherwise add with 7 first to adjust for 'A'

print_nibble:

RCALL SER_send_byte

POP R16 ; retrieves R16

RET

With this subroutine, we can print the lower nibble of R16

main:

RCALL SER_init

LDI R16, 0x0C

RCALL SER_nibble ; prints C

LDI R16, 0x14 ; prints 4

RCALL SER_nibble

Printing Bytes

We can expand this further by printing entire bytes by first printing the upper nibble followed by the lower nibble. In AVR there is an instruction SWAP Rd that swaps the upper 4 bits with the lower 4 bits of Rd.

LDI R16, 0x14

SWAP R16

RCALL SER_nibble ; prints 1 instead

With this, we can complete the hexadecimal printing subroutine.

; Prints R16 as HEX to USART

; R16 is preserved.

SER_hex:

SWAP R16 ; swap to get upper nibble first

RCALL SER_nibble

SWAP R16 ; revert the nibbles back for the lower one

RCALL SER_nibble

RET

main:

RCALL SER_init

LDI R16, 0x3C

RCALL SER_hex ; prints 3C

7. 𝔗𝔥𝔢 ℭ𝔬𝔡𝔢

#define __SFR_OFFSET 0x00

#include "avr/io.h"

.global main

main:

RCALL SER_init

LDI ZH, hi8(opening_msg)

LDI ZL, lo8(opening_msg)

RCALL SER_print

; 16 Bit Addition

LDI ZH, hi8(addition_msg)

LDI ZL, lo8(addition_msg)

RCALL SER_print

; DEC 26983 = HEX 0x6967

LDI R16, 0x69 ; upper byte

LDI R17, 0x67 ; lower byte

; DEC 4882 = HEX 0x1312

LDI R18, 0x13 ; upper byte

LDI R19, 0x12 ; lower byte

ADD R17, R19 ; add lower byte

ADC R16, R18 ; add upper byte + carry from lower

; R16:R17 = 31865

RCALL SER_hex

MOV R16, R17 ; print the lower byte this time

RCALL SER_hex

; 16 Bit Substraction

LDI ZH, hi8(substraction_msg)

LDI ZL, lo8(substraction_msg)

RCALL SER_print

; DEC 26983 = HEX 0x6967

LDI R16, 0x69 ; upper byte

LDI R17, 0x67 ; lower byte

; DEC 4882 = HEX 0x1312

LDI R18, 0x13 ; upper byte

LDI R19, 0x12 ; lower byte

SUB R17, R19 ; substract lower byte

SBC R16, R18 ; substract upper byte - borrow (C) from lower

; R16:R17 = 22101

RCALL SER_hex

MOV R16, R17 ; print the lower byte this time

RCALL SER_hex

; 16 Bit Immediate Addition

LDI ZH, hi8(iaddition_msg)

LDI ZL, lo8(iaddition_msg)

RCALL SER_print

LDI R16, 0x13 ; upper byte

LDI R17, 0x12 ; lower byte

.EQU num, 0x5457 ; immediate variable directive

SUBI R17, lo8(-num) ; 0x12 - -0x57 = 0x12 + 0x57

SBCI R16, hi8(-num) ; 0x13 - -0x54 - C = 0x13 + 0x54 + C

RCALL SER_hex

MOV R16, R17 ; print the lower byte this time

RCALL SER_hex

; 16 Bit Immediate Substraction

LDI ZH, hi8(isubstraction_msg)

LDI ZL, lo8(isubstraction_msg)

RCALL SER_print

LDI R16, 0x67 ; yeah you get the idea atp

LDI R17, 0x69

.EQU num, 0x1312

SUBI R17, lo8(num) ; this time we simply just substract it

SBCI R16, hi8(num) ; no need to be negative :)

RCALL SER_hex

MOV R16, R17 ; print the lower byte this time

RCALL SER_hex

; Multiplication

LDI ZH, hi8(multiplication_msg)

LDI ZL, lo8(multiplication_msg)

RCALL SER_print

LDI R16, 23

LDI R17, 9

MUL R16, R17

MOV R16, R1

RCALL SER_hex

MOV R16, R0

RCALL SER_hex

loop:

RCALL loop

; Initializes USART

; Registers Affected: R24

SER_init:

CLR R24

STS UCSR0A, R24 ; clear UCSR0A register

STS UBRR0H, R24 ; clear UBRR0H register

LDI R24, 103 ; store in UBRR0L 103 value

STS UBRR0L, R24 ; to set baud rate 9600

LDI R24, 1 << RXEN0 | 1 << TXEN0 ; enable RXB & TXB

STS UCSR0B, R24

LDI R24, 1 << UCSZ00 | 1 << UCSZ01 ; asynch, no parity, 1 stop, 8 bits

STS UCSR0C, R24

RET

; Prints character in R16 to USART

; Blocks while UDRE0 is not ready.

; Registers Affected: R24

SER_send_byte:

LDS R24, UCSR0A

SBRS R24, UDRE0 ; test data buffer if data can be sent

RJMP SER_send_byte ; loop back if not ready

STS UDR0, R16 ; sends R16 to USART

RET

; Prints entire message of data pointed in Z until string end (0)

; To fill Z with string message:

; LDI ZH, hi8(message)

; LDI ZL, lo8(message)

; Registers Affected: R16, R24 (SER_send_byte)

SER_print:

LPM R16, Z+ ; load char of string onto R18

CPI R16, 0 ; check if R16 = 0 (end of string)

BREQ exit_SER_print ; if yes, exit

RCALL SER_send_byte ; send the character byte

RJMP SER_print ; loop back & get next character

exit_SER_print:

RET

; Prints the lower nibble of R16

; Registers Affected: R24 (SER_send_byte)

SER_nibble:

PUSH R16 ; preserves R16

ANDI R16, 0x0F ; mask that removes the higher nibble

SUBI R16, -'0' ; add '0' to R16 to represent ASCII '0' - '9'.

CPI R16, '9' + 1 ; compare with '9' + 1 = ':'

BRLT print_nibble ; if no problem just simply print the character

SUBI R16, -7 ; otherwise add with 7 first to adjust for 'A'

print_nibble:

RCALL SER_send_byte

POP R16 ; retrieves R16

RET

; Prints R16 as HEX to USART

; R16 is preserved.

SER_hex:

SWAP R16 ; swap to get upper nibble first

RCALL SER_nibble

SWAP R16 ; revert the nibbles back for the lower one

RCALL SER_nibble

RET

opening_msg:

.byte 10,13 ; new line, carriage return

.ascii "== Literally Einstein and Tesla =="

.byte 0

addition_msg:

.byte 10,13 ; new line, carriage return

.ascii "16 Bit Addition: "

.byte 0

substraction_msg:

.byte 10,13 ; new line, carriage return

.ascii "16 Bit Addition: "

.byte 0

iaddition_msg:

.byte 10,13 ; new line, carriage return

.ascii "16 Bit Immediate Addition: "

.byte 0

isubstraction_msg:

.byte 10,13 ; new line, carriage return

.ascii "16 Bit Immediate Substraction: "

.byte 0

multiplication_msg:

.byte 10,13 ; new line, carriage return

.ascii "Multiplication: "

.byte 0

8. References

“AVR ® Instruction Set Manual AVR ® Instruction Set Manual.” Available: https://ww1.microchip.com/downloads/en/DeviceDoc/AVR-InstructionSet-Manual-DS40002198.pdf

“Lecture 02 – AVR Architecture,” Umbc.edu, 2025. https://eclipse.umbc.edu/robucci/cmpe311/Lectures/L02-AVR_Archetecture/

“How the Arduino memory model works - for AVR · The Coders Corner,” Thecoderscorner.com, 2018. https://www.thecoderscorner.com/electronics/microcontrollers/efficiency/how-arduino-avr-memory-model-works/

“AVR Tutorials - Working With Registers R0 - R31,” www.rjhcoding.com. http://www.rjhcoding.com/avr-asm-registers.php

“Lecture 04 – AVR CPU Registers,” eclipse.umbc.edu. https://eclipse.umbc.edu/robucci/cmpe311/Lectures/L05-AVR_Addressing_Modes/

“AVR Tutorials - The Status Register,” www.rjhcoding.com. http://www.rjhcoding.com/avr-asm-sreg.php

“Assembly via Arduino - Unsigned Arithmetic Operations.” https://akuzechie.blogspot.com/2021/10/assembly-via-arduino-unsigned.html

“AVR Tutorials - Assembly Subroutines,” Rjhcoding.com, 2018. http://www.rjhcoding.com/avr-asm-functions.php

M. Reynolds, “AVR® Stack Register - Developer Help,” Microchip.com, 2023. https://developerhelp.microchip.com/xwiki/bin/view/products/mcu-mpu/8-bit-avr/structure/stack/ (accessed Feb. 25, 2026).

“Lecture 04 – AVR CPU Registers,” Umbc.edu, 2025. https://eclipse.umbc.edu/robucci/cmpe311/Lectures/L04-AVR_CPU_Registers/

Module 5 - Timer

1. Introduction to AVR Timers

1.1. Overview

The ATmega328P is a widely popular 8-bit microcontroller, serving as the "brain" for many embedded systems, most notably the Arduino Uno. Among its most critical peripherals are the Timers. These components allow the microcontroller to perform time-sensitive tasks without stalling the CPU, such as measuring time intervals, generating PWM (Pulse Width Modulation) signals, or triggering specific events at precise moments.

The ATmega328P is equipped with three internal timers:

- Timer0: 8-bit timer (counts from 0 to 255).

- Timer1: 16-bit timer (counts from 0 to 65,535).

- Timer2: 8-bit timer (counts from 0 to 255).

Note: This module only covers Timer0 and Timer1. If you want to know more about Timer2, you can read the ATMega328p Documentation.

1.2. Technical Specifications Overview

While all three timers share similar logic, they differ in resolution and specific features.

| Timer | Resolution | Common Use Case | Pins |

|---|---|---|---|

| Timer0 | 8-bit | Basic time-slicing for multitasking, polling loops, and simple hardware PWM. | PD6 (OC0A), PD5 (OC0B) |

| Timer1 | 16-bit | High-resolution input capture (measuring pulse width), precise frequency generation, and 16-bit event counting. | PB1 (OC1A), PB2 (OC1B) |

| Timer2 | 8-bit | Asynchronous clocking (using a 32kHz crystal on TOSC1/2), real-time counters, and PWM. | PB3 (OC2A), PD3 (OC2B) |

2. Operating Modes

2.1. Normal Mode

In Normal Mode, the timer acts as a simple up-counter. It starts from 0 and increments with every clock pulse (after passing through the prescaler) until it reaches its maximum value (0xFF for 8-bit, 0xFFFF for 16-bit.

Once it hits the maximum, it "rolls over" or overflows back to 0. Upon overflow, the Timer Overflow Flag (TOVn) is set, which can trigger an Interrupt Service Routine (ISR). This is perfect for tracking elapsed time by incrementing a software counter every time an overflow occurs.

Formula for Overflow Frequency:

where N is the prescaler value.

2.2. CTC (Clear Timer on Compare) Mode

CTC Mode is far more precise for generating specific frequencies. Instead of waiting for an overflow at the maximum possible value, the timer counts until it matches a value you pre-defined in the Output Compare Register (OCRnx). As soon as the match occurs, the timer clears itself (resets to 0).

You can configure the timer to "toggle" an output pin automatically when the match occurs, creating a perfect square wave without CPU intervention. For example, to generate a 1 kHz square wave using a 16 MHz clock and a 64 prescaler, you would calculate the required OCR value:

2.3. PWM (Pulse Width Modulation) Mode

PWM Mode is used to simulate an analog output using digital signals. By rapidly switching a pin between HIGH and LOW, you can control the average power delivered to a component.

- Fast PWM: High frequency, suitable for power regulation and LED dimming. The timer counts from 0 to MAX, resetting to 0 immediately. The output pin changes state when the timer reaches the OCR value.

- Phase Correct PWM: Provides a symmetrical waveform by counting up to MAX and then counting back down to 0. This is preferred for motor control as it reduces electromagnetic noise. Duty Cycle: Controlled by the value in the OCR register. A higher value means the signal stays "HIGH" longer within one period.

3. Timer0

3.1. TCNT0 (Timer/Counter 0 Register)

The TCNT0 register is the core component of the 8-bit TIMER0 module. It acts as the actual counter that holds the current timer value. The value of TCNT0 increments (or decrements in certain PWM modes) based on the selected clock source and prescaler.

Users can read from or write to this register at any time. Note that manually writing a value to TCNT0 while the timer is running can cause the timer to "miss" a Compare Match with the OCR0x registers. This happens because the hardware comparison occurs in the clock cycle following a TCNT0 update.

In PWM modes, TCNT0 is constantly compared against OCR0A and OCR0B. When the values match, the output pins (OC0A/OC0B) toggle, clear, or set, depending on the configuration.

3.2. TCCR0 (Timer/Counter 0 Control Register)

In the ATmega328P, the control functionality is split into two registers: TCCR0A and TCCR0B. Together, they define the timer's behavior, including waveform generation, output modes, and clock scaling.

3.2.1. TCCR0A (Control Register A)

- Bit 7:6 - COM0A1:0 (Compare Match Output Mode A): Controls the behavior of the OC0A pin when TCNT0 matches OCR0A.

- Bit 5:4 - COM0B1:0 (Compare Match Output Mode B): Controls the behavior of the OC0B pin when TCNT0 matches OCR0B.

- Bit 1:0 - WGM01:0 (Wave Generation Mode): Combined with WGM02 in TCCR0B to select the timer mode (Normal, CTC, Fast PWM, Phase Correct PWM).

3.2.1.1. COM0x1:0 Description

This table shows the COM0x1:0 functionality when the timer is in a non-PWM mode (normal or CTC):

| COM0x1 | COM0x0 | Description |

|---|---|---|

| 0 | 0 | Normal port operation, OC0x disconnected. |

| 0 | 1 | Toggle OC0x on Compare Match. |

| 1 | 0 | Clear OC0x on Compare Match (Set output to low). |

| 1 | 1 | Set OC0x on Compare Match (Set output to high). |

3.2.1.2. WGM02:0 Description

This table shows how the WGM02:0 bits affect the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of waveform generation to be used:

| WGM02 | WGM01 | WGM00 | Timer/Counter Mode of Operation | TOP | Update of OCRx at | TOV Flag Set on |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | Normal | 0xFF | Immediate | MAX |

| 0 | 0 | 1 | PWM, phase correct | 0xFF | TOP | BOTTOM |

| 0 | 1 | 0 | CTC | OCRA | Immediate | MAX |

| 0 | 1 | 1 | Fast PWM | 0xFF | BOTTOM | MAX |

| 1 | 0 | 0 | Reserved | — | — | — |

| 1 | 0 | 1 | PWM, phase correct | OCRA | TOP | BOTTOM |

| 1 | 1 | 0 | Reserved | — | — | — |

| 1 | 1 | 1 | Fast PWM | OCRA | BOTTOM | TOP |

Notes:

- MAX: 0xFF

- BOTTOM: 0x00

- Update of OCRx at: When the hardware actually updates the value of the Compare Register if you change it while the timer is running.

3.2.2. TCCR0B (Control Register B)

- Bit 7 - FOC0A (Force Output Compare A): Only active in non-PWM modes. Writing

1forces an immediate match on OC0A. - Bit 6 - FOC0B (Force Output Compare B): Only active in non-PWM modes. Writing

1forces an immediate match on OC0B. - Bit 3 - WGM02 (Waveform Generation Mode): Works with WGM01:0 to set the mode.

- Bit 2:0 - CS02:0 (Clock Select): Sets the prescaler or selects an external clock source.

3.2.2.1. CS02:0 Prescaler Settings

| CS02 | CS01 | CS00 | Description |

|---|---|---|---|

| 0 | 0 | 0 | No clock source (Timer/Counter stopped) |

| 0 | 0 | 1 | clk / 1 (No prescaling) |

| 0 | 1 | 0 | clk / 8 (From prescaler) |

| 0 | 1 | 1 | clk / 64 (From prescaler) |

| 1 | 0 | 0 | clk / 256 (From prescaler) |

| 1 | 0 | 1 | clk / 1024 (From prescaler) |

| 1 | 1 | 0 | External clock source on T0 pin. Clock on falling edge. |

| 1 | 1 | 1 | External clock source on T0 pin. Clock on rising edge. |

3.3. TIFR0 (Timer/Counter 0 Interrupt Flag Register)

- Bit 2 - OCF0B (Output Compare Flag B): Set to

1when TCNT0 matches the value in OCR0B. - Bit 1 - OCF0A (Force Output Compare A): Set to

1when TCNT0 matches the value in OCR0A. - Bit 0 - TOV0 (Timer Overflow Flag): Set to

1when the timer overflows (reaches its MAX value and restarts from 0).

4. Timer1

4.1. TCNT1 (Timer/Counter Register)

TCNT1 is functionally the same as TCNT0, serving as the core counter for its respective module, with several significant additions and architectural differences. TCNT1 is a 16-bit register divided into two 8-bit register, TCNT1H (high byte) and TCNT1L (low byte). This allows it to count from 0 to 65,535, providing much higher precision and longer timing.

TCNT1 includes a specialized Input Capture feature not found in Timer0. When a signal event occurs on the ICP1 pin, the current value of TCNT1 is instantly copied into the ICR1 register. This is used to measure external pulse widths with high accuracy.

4.2. TCCR1 (Timer/Counter 1 Control Register)

4.2.1. TCCR1A (Control Register A)

- Bit 7:6 - COM10A1:0 (Compare Match Output Mode A): Controls the behavior of the OC1A pin when TCNT1 matches OCR1A.

- Bit 5:4 - COM1B1:0 (Compare Match Output Mode B): Controls the behavior of the OC1B pin when TCNT1 matches OCR1B.

- Bit 1:0 - WGM11:0 (Wave Generation Mode): Combined with WGM13:12 in TCCR1B to select one of 16 available modes.

4.2.1.1. COM1x1:0 Description

This table shows the COM1x1:0 functionality when the timer is in a non-PWM mode (normal or CTC):

| COM1x1 | COM1x0 | Description |

|---|---|---|

| 0 | 0 | Normal port operation, OC1x disconnected. |

| 0 | 1 | Toggle OC1x on Compare Match. |

| 1 | 0 | Clear OC1x on Compare Match (Set output to low). |

| 1 | 1 | Set OC1x on Compare Match (Set output to high). |

4.2.1.2. WGM13:0 Description

This table shows how the WGM13:0 bits affect the counting sequence of the counter, the source for maximum (TOP) counter value, and what type of waveform generation to be used:

| Mode | WGM13 | WGM12 | WGM11 | WGM10 | Timer/Counter Mode of Operation | TOP | Update of OCR1x at | TOV1 Flag Set on |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | Normal | 0xFFFF | Immediate | MAX |

| 1 | 0 | 0 | 0 | 1 | PWM, phase correct, 8-bit | 0x00FF | TOP | BOTTOM |

| 2 | 0 | 0 | 1 | 0 | PWM, phase correct, 9-bit | 0x01FF | TOP | BOTTOM |

| 3 | 0 | 0 | 1 | 1 | PWM, phase correct, 10-bit | 0x03FF | TOP | BOTTOM |

| 4 | 0 | 1 | 0 | 0 | CTC | OCR1A | Immediate | MAX |

| 5 | 0 | 1 | 0 | 1 | Fast PWM, 8-bit | 0x00FF | BOTTOM | TOP |

| 6 | 0 | 1 | 1 | 0 | Fast PWM, 9-bit | 0x01FF | BOTTOM | TOP |

| 7 | 0 | 1 | 1 | 1 | Fast PWM, 10-bit | 0x03FF | BOTTOM | TOP |

| 8 | 1 | 0 | 0 | 0 | PWM, phase and frequency correct | ICR1 | BOTTOM | BOTTOM |

| 9 | 1 | 0 | 0 | 1 | PWM, phase and frequency correct | OCR1A | BOTTOM | BOTTOM |

| 10 | 1 | 0 | 1 | 0 | PWM, phase correct | ICR1 | TOP | BOTTOM |

| 11 | 1 | 0 | 1 | 1 | PWM, phase correct | OCR1A | TOP | BOTTOM |

| 12 | 1 | 1 | 0 | 0 | CTC | ICR1 | Immediate | MAX |

| 13 | 1 | 1 | 0 | 1 | (Reserved) | — | — | — |

| 14 | 1 | 1 | 1 | 0 | Fast PWM | ICR1 | BOTTOM | TOP |

| 15 | 1 | 1 | 1 | 1 | Fast PWM | OCR1A | BOTTOM | TOP |

4.2.2. TCCR1B (Control Register B)

- Bit 7 - ICNC1 (Input Capture Noise Canceler): When set to

1, a digital filter is activated on the ICP1 pin. It requires four matching cycles to trigger, reducing noise spikes. - Bit 6 - ICES1 (Input Capture Edge Select): Selects which edge triggers a capture on the ICP1 pin.

1= Rising edge;0= Falling edge. - Bit 3 - WGM13:2 (Waveform Generation Mode): Works with WGM11:0 to set the mode.

- Bit 2:0 - CS12:0 (Clock Select): Sets the prescaler or selects an external clock source.

4.2.2.1. CS02:0 Prescaler Settings

| CS12 | CS11 | CS10 | Description |

|---|---|---|---|

| 0 | 0 | 0 | No clock source (Timer/Counter stopped) |

| 0 | 0 | 1 | clk / 1 (No prescaling) |

| 0 | 1 | 0 | clk / 8 (From prescaler) |

| 0 | 1 | 1 | clk / 64 (From prescaler) |

| 1 | 0 | 0 | clk / 256 (From prescaler) |

| 1 | 0 | 1 | clk / 1024 (From prescaler) |

| 1 | 1 | 0 | External clock source on T0 pin. Clock on falling edge. |

| 1 | 1 | 1 | External clock source on T0 pin. Clock on rising edge. |

4.2.3. TCCR1C (Control Register C)

- Bit 7 - FOC1A (Force Output Compare A): Only active in non-PWM modes. Writing

1forces an immediate match on OC1A. - Bit 6 - FOC1B (Force Output Compare B): Only active in non-PWM modes. Writing

1forces an immediate match on OC1B.

4.3. TIFR1 (Timer/Counter 1 Interrupt Flag Register)

- Bit 5 - ICF1 (Input Capture Flag): Set to

1when a capture event occurs on the ICP1 pin. - Bit 2 - OCF1B (Output Compare Flag B): Set to

1when TCNT1 matches the value in OCR1B. - Bit 1 - OCF1A (Force Output Compare A): Set to

1when TCNT1 matches the value in OCR1A. - Bit 0 - TOV1 (Timer Overflow Flag): Set to

1when the timer overflows (reaches its MAX value and restarts from 0).

5. Delay Using Timers

5.1. Delay Calculation in Normal Mode

In Normal Mode, the timer always counts up to its maximum value and then overflows. To get a specific delay, you preload the TCNTn register with a starting value so it only has to count a specific number of steps before overflowing.

Here is the formula to find the required preload value:

For example, if we want to create a 1ms delay using Timer0 with 1/64 presacaler:

5.2. Delay Calculation in CTC Mode

In CTC (Clear Timer on Compare) Mode, the timer is much easier to use for delays because the hardware automatically resets the counter to zero when it reaches a target value stored in the OCRnx (Output Compare Register).

Here is the formula to find the value to put in OCRnx register:

For example, if we want to create a 1ms delay using Timer0 with 1/64 presacaler:

6. Der Code

6.1. Code Example 1 (Timer0)

This code toggles PD5 every 0.5s. The delay_timer0 subroutine uses Timer0 in CTC Mode with a 1024 prescaler and a compare value of 156, creating a 10ms hardware delay per call. This subroutine is called 50 times using software loop with R18 as the counter.

;------------------------

; Assembly Code

;------------------------

#define __SFR_OFFSET 0x00

#include "avr/io.h"

;------------------------

.global main

;===============================================================

main:

LDI R16, 0b00100000 ; to toggle PD5

LDI R17, 0b00000000

;--------------------------------------------

SBI DDRD, 5 ; set PD5 for o/p

OUT PORTD, R17 ; PD5 = 0

;--------------------------------------------

LDI R18, 50 ; set loop counter

l1: RCALL delay_timer0 ; apply delay via timer0

DEC R18

BRNE l1 ; & go back & repeat

;--------------------------------------------

EOR R17, R16 ; R17 = R17 XOR R16

OUT PORTD, R17 ; toggle PD5

LDI R18, 50 ; re-set loop counter

RJMP l1 ; go back & repeat toggle

;===============================================================

delay_timer0: ; ~10ms delay via Timer0

;---------------------------------------------------------

CLR R20

OUT TCNT0, R20 ; initialize timer0 with count=0

LDI R20, 156

OUT OCR0A, R20 ; OCR0 = 9

LDI R20, 0b00000010

OUT TCCR0A, R20

LDI R20, 0b00000101

OUT TCCR0B, R20 ; timer0: CTC mode, prescaler 1024

;---------------------------------------------------------

l2: IN R20, TIFR0 ; get TIFR0 byte & check

SBRS R20, OCF0A ; if OCF0=1, skip next instruction

RJMP l2 ; else, loop back & check OCF0 flag

;---------------------------------------------------------

CLR R20

OUT TCCR0B, R20 ; stop timer0

;---------------------------------------------------------

LDI R20, (1<<OCF0A)

OUT TIFR0, R20 ; clear OCF0 flag

RET

6.2. Code Example 2 (Timer1)

This code toggles PD5 every 0.5s (just like Code Example 1). The delay_timer1 subroutine uses Timer1 in Normal Mode with a 1024 prescaler and a preload value of 57724, creating a 500ms hardware delay per call.

;------------------------

; Assembly Code

;------------------------

#define __SFR_OFFSET 0x00

#include "avr/io.h"

;------------------------

.global main

;===============================================================

main:

LDI R16, 0b00100000 ; to toggle PD5

LDI R17, 0b00000000

;---------------------------------------------

SBI DDRD, 5 ; set PD5 for o/p

OUT PORTD, R17 ; PD5 = 0

;---------------------------------------------

l1: RCALL delay_timer1 ; 0.5 sec delay via timer1

;---------------------------------------------

EOR R17, R16 ; R17 = R17 XOR R16

OUT PORTD, R17 ; toggle PD5

LDI R18, 61 ; re-set loop counter

RJMP l1 ; go back & repeat toggle

;===============================================================

delay_timer1: ; 0.5 sec delay via timer1

;-------------------------------------------------------

.EQU value, 57724 ; value to give 0.5 sec delay

LDI R20, hi8(value)

STS TCNT1H, R20

LDI R20, lo8(value)

STS TCNT1L, R20 ; initialize counter TCNT1 = value

;-------------------------------------------------------

LDI R20, 0b00000000

STS TCCR1A, R20

LDI R20, 0b00000101

STS TCCR1B, R20 ; normal mode, prescaler = 1024

;-------------------------------------------------------

l2: IN R20, TIFR1 ; get TIFR1 byte & check

SBRS R20, TOV1 ; if TOV1=1, skip next instruction

RJMP l2 ; else, loop back & check TOV1 flag

;-------------------------------------------------------

LDI R20, 1<<TOV1

OUT TIFR1, R20 ; clear TOV1 flag

;-------------------------------------------------------

LDI R20, 0b00000000

STS TCCR1B, R20 ; stop timer1

RET

Module 6 - Interrupt

1. Introduction to Interrupt

An interrupt is a mechanism used in microcontroller programming to pause the execution of the current program and call a specific routine or function when a particular event occurs. These events, defined by the programmer, can range from a specific condition on an input pin to a timer overflow or other hardware-defined triggers. Once the routine or function finishes executing, the program resumes from the exact point where it was interrupted.

The Arduino Uno (ATMega328P) provides two primary types of interrupts: External Interrupts and Timer Interrupts. While their functions and triggers differ, they share the same goal: interrupting the main program flow to handle specific events immediately.

External Interrupt

An External Interrupt is triggered by a change in the voltage level on specific input pins of the microcontroller. On the Arduino Uno, there are two pins dedicated to external interrupts: Pin 2 and Pin 3. These are the most commonly used pins when implementing interrupts via the Arduino programming language.

External Interrupts: INT0 and INT1

While the Arduino IDE refers to these simply as Pin 2 and Pin 3, the ATMega328P datasheet identifies them as INT0 and INT1. These are hardware-level designations that correspond to specific physical pins.

- INT0 (Digital Pin 2): This is the first external interrupt. It has a higher priority in the Interrupt Vector Table than INT1, meaning if both occur at the exact same time, the microcontroller will handle INT0 first.

- INT1 (Digital Pin 3): This is the second external interrupt.

Trigger Modes

Both INT0 and INT1 can be configured to trigger the Interrupt Service Routine (ISR) based on four specific signal states:

- LOW: Triggered whenever the pin is at a logic low level.

- CHANGE: Triggered whenever the pin changes value (High to Low or Low to High).

- RISING: Triggered specifically when the pin goes from Low to High.

- FALLING: Triggered specifically when the pin goes from High to Low.

Internal Interrupt

An Internal Interrupt is triggered by modules located inside the microcontroller itself. In the ATMega328P, these are generated by timers and are referred to as Timer Interrupts. A Timer Interrupt is specifically triggered by a timer overflow. The Arduino Uno features three internal timers: Timer0, Timer1, and Timer2. (For more details on how timers operate, please refer to the previous module).

To expand on the specific hardware components of the ATMega328P (the heart of the Arduino Uno), we need to look at how the microcontroller labels and manages these specific interrupt sources.

Internal Interrupts: Timer0, Timer1, and Timer2

The Arduino Uno has three hardware timers, each capable of generating interrupts. These are essential for tasks that require precise timing without blocking the void loop().

1. Timer0 (8-bit)

- Role: This timer is used by the Arduino internal functions like

delay(),millis(), andmicros(). - Interrupt Potential: It can trigger an Overflow Interrupt (when the counter hits 255 and resets to 0) or a Compare Match Interrupt.

- Note: Modifying Timer0 registers directly is generally discouraged because it will break the Arduino's built-in time-keeping functions.

2. Timer1 (16-bit)